a leap ahead

**22** austria**micro**systems

DataSheet

## AS1710/AS1712 High-Output-Drive, 10MHz, 10V/µs, Rail-to-Rail I/O Op Amps with Shutdown

## **1** General Description

The AS1710/AS1712 are low-offset, high-output CMOS op amps that deliver 200mA of peak output current from a single supply (2.7 to 5.5V).

These devices were specifically designed to drive typical headset levels ( $32\Omega$ ), as well as bias RF power amplifiers for wireless handset applications.

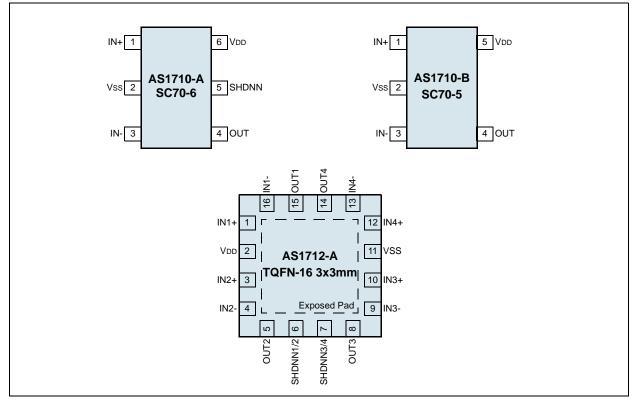

The devices are available as the standard products shown in Table 1. See also Ordering Information on page 16.

| Table 1. | Standard | Products |

|----------|----------|----------|

|----------|----------|----------|

| Model   | Description Package            |                  |

|---------|--------------------------------|------------------|

| AS1710A | Single Op Amp<br>with Shutdown | SC70-6           |

| AS1710B | Single Op Amp                  | SC70-5           |

| AS1712A | Quad Op Amp<br>w/Shutdown      | TQFN-16<br>3x3mm |

These rail-to-rail I/O, wide-bandwidth amplifiers exhibit a high slew rate of  $10V/\mu s$  and a gain-bandwidth product of 10MHz.

The integrated shutdown feature (not included in B versions) drives the output low.

These devices operate over the entire automotive temperature range (-40°C to +125°C).

## 2 Key Features

- Constant Output Drive Capability: 50mA

- Rail-to-Rail Input and Output

- Supply Current: 1.6mA

- Single-Supply Operation: 2.7 to 5.5V

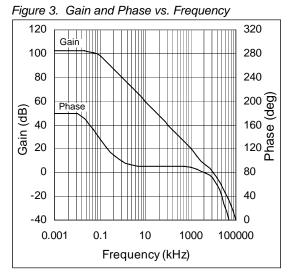

- Gain-Bandwidth Product: 10MHz

- High Slew Rate: 10V/µs

- Voltage Gain: 100dB (RLOAD = 100kΩ)

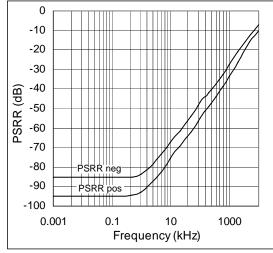

- Power-Supply Rejection Ratio: -85dB

- No Phase Reversal for Overdriven Inputs

- Unity-Gain Stable for Capacitive Loads: Up to 100pF

- Shutdown Mode (AS1710A) Current: 1nA typ

- Package Types:

- SC70-6

- SC70-5

- TQFN-16 3x3mm

## **3** Applications

The devices are ideal for portable/battery-powered audio applications, portable headphone speaker drivers ( $32\Omega$ ), hands-free mobile phone kits, TFT panels, sound ports/cards, set-top boxes, biasing controls, DAC converter buffers, transformer/line drivers, motor drivers, and any other battery-operated audio device.

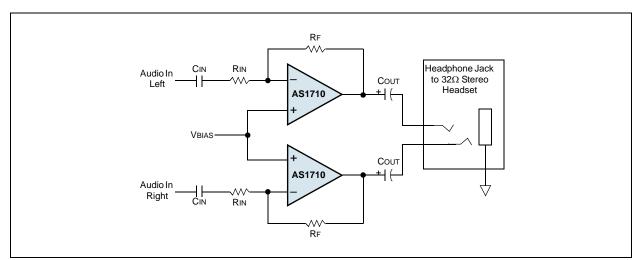

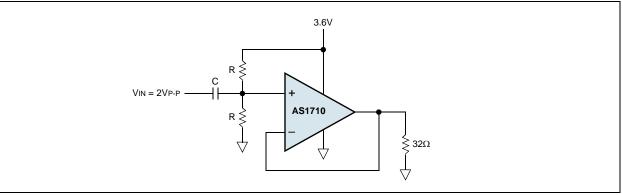

Figure 1. Typical Application

# 4 Pinout

### **Pin Assignments**

Figure 2. Pin Assignments (Top View)

### **Pin Descriptions**

Table 2. Pin Descriptions

| Pin Number   | Pin Name    | Description                                                                                                                                              |

|--------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | IN+         | Non-inverting Input                                                                                                                                      |

|              | IN-         | Inverting Input                                                                                                                                          |

|              | Vdd         | Positive Supply Input                                                                                                                                    |

| See Figure 2 | Vss         | <b>Negative Supply Input.</b> This pin must be connected to ground in single-supply applications.                                                        |

|              | SHDNN       | Active Low Shutdown Control                                                                                                                              |

|              | OUT         | Amplifier Output                                                                                                                                         |

|              | Exposed Pad | <b>Exposed Pad.</b> This pin also functions as a heat sink. Solder it to a large pad or to the circuit-board ground plane to maximize power dissipation. |

# **5** Absolute Maximum Ratings

Stresses beyond those listed in Table 3 may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in Electrical Characteristics on page 4 is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Table 3. | Absolute | Maximum | Ratings |

|----------|----------|---------|---------|

|----------|----------|---------|---------|

| Parameter                            |                  | Min          | Max          | Units | Comments                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------|------------------|--------------|--------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Supply Voltage (VDD to Vss)          |                  |              | +7           | V     |                                                                                                                                                                                                                                                                                                                           |

| Supply Voltage (All Other Pins)      |                  | Vss<br>- 0.3 | VDD<br>+ 0.3 | V     |                                                                                                                                                                                                                                                                                                                           |

| Output Short-Circuit D<br>VDD or Vss | uration to       |              | 1            | S     |                                                                                                                                                                                                                                                                                                                           |

| Continuous Power                     | SC70-5           |              | 247          | mW    | Derate at 31mW/ºC above 70°C                                                                                                                                                                                                                                                                                              |

| Dissipation                          | SC70-6           |              | 245          | 11177 | Derate at 31mW/ºC above 70ºC                                                                                                                                                                                                                                                                                              |

| Thermal Resistance <sub>OJA</sub>    | TQFN-16<br>3x3mm |              | 33           | °C/W  | on PCB                                                                                                                                                                                                                                                                                                                    |

| Operating Temperatur                 | re Range         | -40          | +125         | °C    |                                                                                                                                                                                                                                                                                                                           |

| Storage Temperature                  | e Range          | -65          | +150         | °C    |                                                                                                                                                                                                                                                                                                                           |

| Junction Tempera                     | ature            |              | +150         | °C    |                                                                                                                                                                                                                                                                                                                           |

| Package Body Temp                    | perature         |              | +260         | °C    | The reflow peak soldering temperature (body<br>temperature) specified is in accordance with<br><i>IPC/JEDEC J-STD-020C "Moisture/Reflow</i><br><i>Sensitivity Classification for Non-Hermetic</i><br><i>Solid State Surface Mount Devices".</i><br>The lead finish for Pb-free leaded packages is<br>matte tin (100% Sn). |

# **6 Electrical Characteristics**

## **DC Electrical Characteristics**

VDD = 2.7V, VSS = 0V, VCM = VDD/2, VOUT = VDD/2, RLOAD = Infinite, VSHDNN = VDD, TAMB = -40 to  $+125^{\circ}C$ . Typical values at TAMB =  $25^{\circ}C$ .

Table 4. DC Electrical Characteristics

| Symbol        | Parameter                                      | Conditi                             | on                           | Min              | Тур               | Max               | Unit |       |

|---------------|------------------------------------------------|-------------------------------------|------------------------------|------------------|-------------------|-------------------|------|-------|

| Vdd           | Supply Voltage Range                           | Inferred from Po<br>Rejection Ra    |                              | 2.7              |                   | 5.5               | V    |       |

| VOFFSET       | Input Offset Voltage                           |                                     |                              | -3               | 0.6               | +3                | mV   |       |

| <b>I</b> BIAS | Input Bias Current                             | VCM = VSS                           | to Vdd                       |                  | 50 <sup>1</sup>   |                   | pА   |       |

| IOFFSET       | Input Offset Current                           | VCM = VSS                           | to Vdd                       |                  | 50 <sup>1</sup>   |                   | pА   |       |

| Rin           | Input Resistance                               |                                     |                              |                  | 1000 <sup>1</sup> |                   | MΩ   |       |

| Vсм           | Common Mode Input<br>Voltage Range             | Inferred from Cor<br>Rejection F    |                              | Vss              |                   | Vdd               | V    |       |

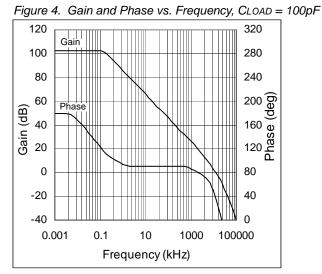

| CMRR          | Common Mode<br>Rejection Ratio                 | Vss < Vcm                           | < Vdd                        | -45              | -70               |                   | dB   |       |

| PSRR          | Power Supply Rejection Ratio                   | VDD = 2.7 to                        | o 5.5V                       | -70              | -85               |                   | dB   |       |

| Rout          | Shutdown Output Impedance                      | VSHDNN = 0V (A                      | -Versions)                   |                  | 130 <sup>1</sup>  |                   | Ω    |       |

| VOUT-SHDNN    | Shutdown Output Voltage                        | VSHDNN = 0V, RLOAD<br>(A-Versio     |                              |                  | 170               | 300               | mV   |       |

|               |                                                |                                     | $RLOAD = 100k\Omega$         | 85               | 100               |                   | dB   |       |

| AVOL          | Large Signal Voltage Gain                      | Vss + 0.20V < Vout <<br>VDD - 0.20V | $RLOAD = 2k\Omega$           | 79               | 92                |                   |      |       |

|               |                                                |                                     | $RLOAD = 200\Omega$          | 69               | 80                |                   |      |       |

|               |                                                | ., .,                               | $RLOAD = 32\Omega$           |                  | 350               | 650               | mV   |       |

| Vout          | Output Voltage Swing                           | Vdd - Voh or<br>Vol - Vss           | $R$ LOAD = 200 $\Omega$      |                  | 70                | 120               |      |       |

|               |                                                |                                     | $RLOAD = 2k\Omega$           |                  | 9                 | 20                |      |       |

|               | Output Voltage                                 | Vdd - Voh or                        | ILOAD = 10mA,<br>VDD = 2.7V  |                  | 55                | 100               | mV   |       |

|               | Output voltage                                 | Vol - Vss                           | ILOAD = 30mA,<br>VDD = 5V    |                  | 100               | 180               | IIIV |       |

| Ιουτ          | Output Source/Sink Current                     | VDD = 2.<br>V- = VCM, V+ = \        | 7V,<br>/см±100mV             |                  | 100               |                   | mA   |       |

| 1001          |                                                |                                     | VDD = 5.<br>V- = VCM, V+ = \ | 0V,<br>/см±100mV |                   | 200               |      | THU V |

| ldd           | Quiescent Supply Current per                   | VDD = 2.7V, VC                      | M = VDD/2                    |                  | 1.6               | 3.2               | mA   |       |

| עטו           | OpAmp Output                                   | VDD = 5.0V, VCM = VDD/2             |                              |                  | 2.3               | 4.6               | ШA   |       |

| IDD-SHDNN     | Shutdown Supply Current per OpAmp (A-Versions) | VSHDNN = 0V                         | VDD = 2.7V                   |                  | 1                 | 2000 <sup>1</sup> | nA   |       |

|               | SHDNN Logic Threshold                          | Shutdown                            | Mode                         |                  | Vss +<br>0.3      |                   | V    |       |

|               | (A-Versions)                                   | Normal Ope                          | eration                      |                  | Vdd -<br>0.3      |                   | v    |       |

|               | SHDNN Input Bias Current                       | Vss < Vshdnn < Vd                   | D (A-Versions)               |                  | 50 <sup>1</sup>   |                   | pА   |       |

1. Guaranteed by design.

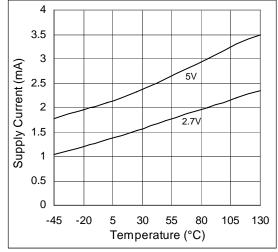

## **AC Electrical Characteristics**

VDD = 2.7V, VSS = 0V, VCM = VDD/2, VOUT = VDD/2, RLOAD = Infinite, VSHDNN = VDD, TAMB = -40 to  $+125^{\circ}C$ . Typical values at TAMB = 25°C.

Table 5. AC Electrical Characteristics

| Symbol          | Parameter                               | Conditions                             | Min | Тур  | Max | Units |

|-----------------|-----------------------------------------|----------------------------------------|-----|------|-----|-------|

| GBWP            | Gain-Bandwidth Product                  | VCM = VDD/2                            |     | 10   |     | MHz   |

| FPBW            | Full-Power Bandwidth                    | Vout = 2VP-P, Vdd = 5V                 |     | 2.5  |     | MHz   |

| SR              | Slew Rate                               |                                        |     | 10   |     | V/µs  |

| PM              | Phase Margin                            |                                        |     | 70   |     | deg   |

| GM              | Gain Margin <sup>1</sup>                |                                        |     | 15   |     | dB    |

| THD+N           | Total Harmonic Distortion<br>Plus Noise | f = 10kHz, Vout = 2VP-P, Avcl = 1V/V   |     | 0.05 |     | %     |

| CIN             | Input Capacitance                       |                                        |     | 6    |     | pF    |

| 0.0             |                                         | f = 1kHz                               |     | 15   |     | ņV/   |

| en              | Voltage-Noise Density <sup>1</sup>      | f = 10kHz                              |     | 10   |     | √Hz   |

|                 | Capacitive-Load Stability               | AvcL = 1V/V, no sustained oscillations |     | 100  |     | pF    |

| tSHDN           | Shutdown Time<br>(AS1710A)              |                                        |     | 1    |     | μs    |

| <b>t</b> ENABLE | Enable Time from Shutdown<br>(AS1710A)  |                                        |     | 7    |     | μs    |

| tON             | Power-Up Time                           |                                        |     | 20   |     | ns    |

1. Guaranteed by design.

# **7** Typical Operating Characteristics

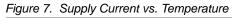

VDD = 2.7V; VSS = 0V, VCM = VDD/2, VOUT = VDD/2,  $RLOAD = \infty$ , VSHDNN = VDD TAMB = +25°C (unless otherwise specified).

Figure 5. PSRR vs. Frequency

Figure 6. CMRR vs. Frequency

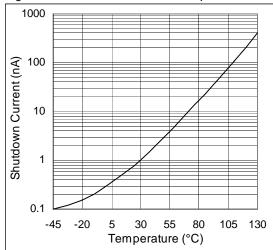

Figure 8. Shutdown Current vs. Temperature

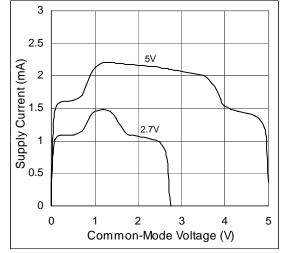

Figure 9. Supply Current vs. Common-Mode Voltage

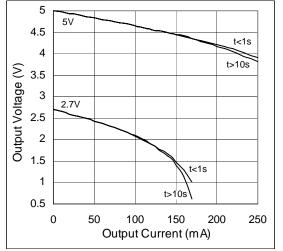

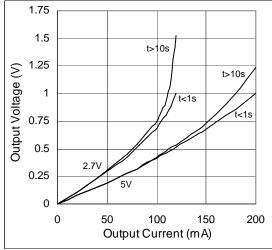

Figure 11. Output Voltage vs. Output Current, sourcing

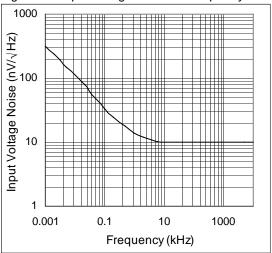

Figure 10. Input Voltage Noise vs. Frequency

Figure 12. Output Voltage vs. Output Current, sinking

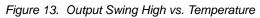

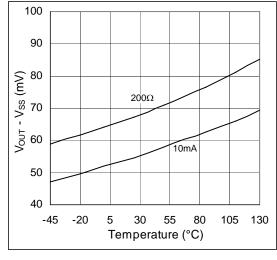

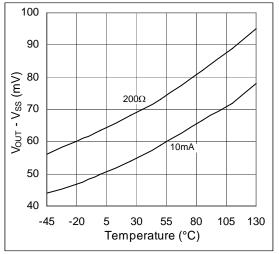

Figure 14. Output Swing Low vs. Temperature

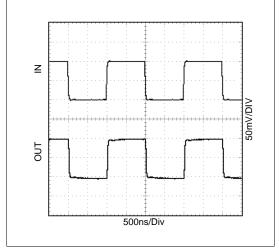

Figure 15. Transient Response, 100mV, 10pF load

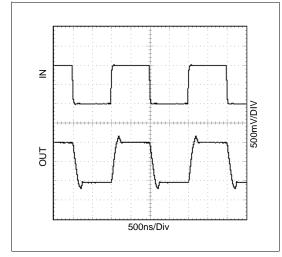

Figure 17. Transient Response, 1V, 10pF load

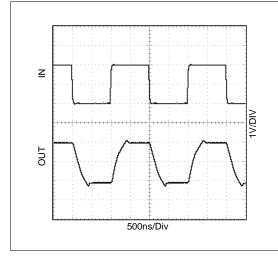

Figure 16. Transient Response, 100mV, 100pF load

Figure 18. Transient Response, 1V, 100pF load

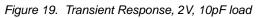

Figure 20. Transient Response, 2V, 100pF load

## 8 Application Information

### Package Power Dissipation

**Caution:** Due to the high output current drive, this op amp can exceed the absolute maximum power-dissipation rating. Normally, when peak current is less than or equal to 40mA the maximum package power dissipation is not exceeded for any of the package types offered.

The absolute maximum power-dissipation rating of each package should always be verified. (EQ 1) gives an approximation of the package power dissipation:

$$PPACKAGEDISS \cong VRMS IRMS COS\theta$$

(EQ 1)

#### Where:

VRMs is the RMS voltage from VDD to VOUT when sourcing current, and from VOUT to Vss when sinking current. IRMs is the RMS current flowing in or out of the op amp and the load.

$\theta$  is the phase difference between the voltage and the current. For resistive loads, COS $\theta$  = 1.

VRMS can be calculated as:

$$VRMS \cong (VDD - VDC) + VPEAK / \sqrt{2}$$

(EQ 2)

#### Where:

VDC is the DC component of the output voltage.

VPEAK is the highest positive excursion of the AC component of the output voltage.

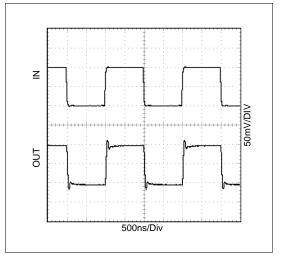

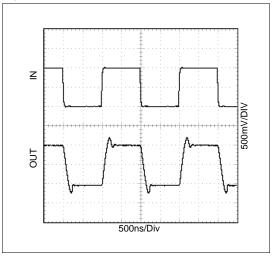

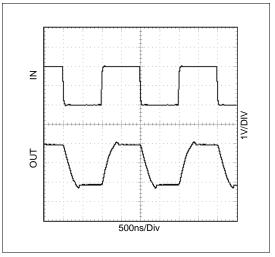

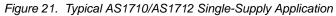

For the circuit shown in Figure 21:

IRMS can be calculated as:

IRMS

$$\cong$$

IDC + (IPEAK/ $\sqrt{2}$ ) (EQ 3)

#### Where:

IDC is the DC component of the output current.

IPEAK is the highest positive excursion of the AC component of the output current.

For the circuit shown in Figure 21:

$IRMS = (1.8V/32\Omega) + (1.0V/32\Omega)/\sqrt{2} = 78.4mARMS$

Therefore, for the circuit in Figure 21 the package power dissipation can be calculated as:

PPACKAGEDISS = VRMS IRMS  $COS\theta$  = 196mW

Adding a coupling capacitor improves the package power dissipation because there is no DC current to the load, as shown in Figure 22 on page 10.

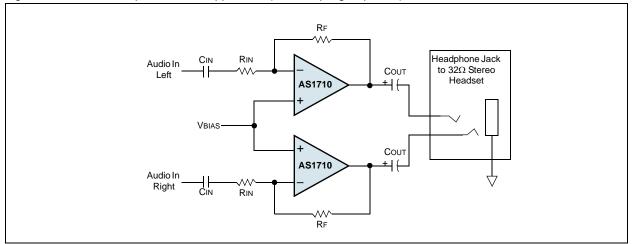

### 60mW Single-Supply Stereo Headphone Driver

Two AS1710 amplifiers can be used as a single-supply, stereo headphone driver. The circuit shown in Figure 22 can deliver 60mW per channel with 1% distortion from a single 5V supply.

Figure 22. Stereo Headphone Driver Application (with Coupling Capacitor)

In Figure 22, CIN and RIN form a high-pass filter that removes the DC bias from the incoming signal. The -3dB point of the high-pass filter is given by:

$$f_{-3dB} = 1/(2\pi R i N C i N) \tag{EQ 4}$$

Choose gain-setting resistors RIN and RF according to the amount of desired gain, keeping in mind the maximum output amplitude.

COUT blocks the DC component of the amplifier output, preventing DC current flowing to the load. The output capacitor and the load impedance form a high-pass filter with the -3dB point determined by:

$$f-3dB = 1/(2\pi R LOADCOUT)$$

(EQ 5)

For a 32Ω load, a 100µF aluminum electrolytic capacitor gives a low-frequency pole at 50Hz.

#### Rail-to-Rail Input Stage

The AS1710/AS1712 CMOS op amps have parallel connected N- and P-channel differential input stages that combine to accept a common-mode range extending to both supply rails. The N-channel stage is active for common-mode input voltages typically greater than (Vss + 1.2V), and the p-channel stage is active for common-mode input voltages typically less than (VDD - 1.2V).

### **Rail-to-Rail Output Stage**

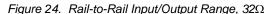

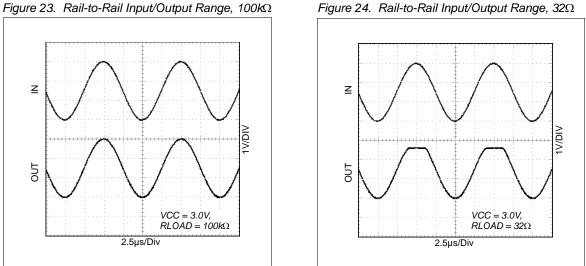

The minimum output is within millivolts of ground for single- supply operation, where the load is referenced to ground (Vss). Figure 23 shows the input voltage range and the output voltage swing of an AS1710 connected as a voltage follower. The maximum output voltage swing is load dependent although it is guaranteed to be within 500mV of the positive rail (VDD = 2.7V) even with maximum load ( $32\Omega$  to ground).

Note: The absolute maximum ratings (see page 3) for power dissipation and output short-circuit duration (10s, max) must be adhered to since the output current can exceed 200mA (see Typical Operating Characteristics on page 6).

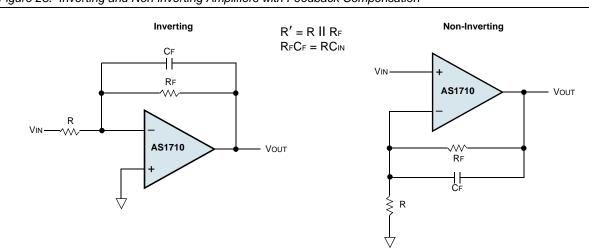

### Input Capacitance

The parallel-connected differential input stages for rail-to-rail operation results in relatively large input capacitance CIN (6pF typ). This introduces a pole at frequency  $(2\pi R'C_{IN})$ , where R' is the parallel combination of the gain-setting resistors for the inverting or non-inverting amplifier configuration (Figure 25). If the pole frequency is less than or comparable to the unity-gain bandwidth (10MHz), the phase margin is reduced, and the amplifier exhibits degraded AC performance through either ringing in the step response or sustained oscillations.

Figure 25. Inverting and Non-inverting Amplifiers with Feedback Compensation

The pole frequency is 10MHz when R' =  $2k\Omega$ . To maximize stability, R' <<  $2k\Omega$  is recommended.

To improve step response when  $R' > 2k\Omega$ , connect a small capacitor (CF) between the inverting input and output. CF can be calculated by:

$$CF = 6(R/RF) [pf]$$

(EQ 6)

Where:

RF is the feedback resistor. R is the gain-setting resistor. Data Sheet - Application Information

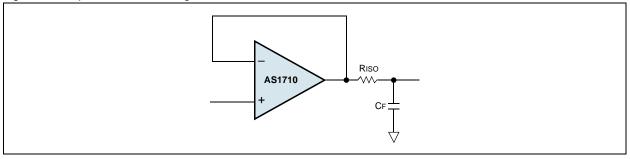

### **Driving Capacitive Loads**

The AS1710/AS1712 amplifiers have a high tolerance for capacitive loads, and are stable with capacitive loads up to 100pF.

Figure 26 shows a typical non-inverting capacitive-load driving circuit in the unity-gain configuration.

Figure 26. Capacitive-Load Driving Circuit

**Note:** Resistor RISO improves the circuit's phase margin by isolating the load capacitor from the AS1710/AS1712 output.

#### Power-Up

The AS1710/AS1712 typically settle within 5µs after power-up.

#### Shutdown

When SHDNN (not included in B versions) is pulled low, supply current drops to  $0.5\mu$ A (per amplifier, VDD = 2.7V), the amplifiers are disabled, and their outputs are driven to Vss. Because the outputs are actively driven to Vss in shut-down, any pullup resistor on the output causes a current drain from the supply.

Note: Pulling SHDNN high enables the amplifier. In the AS1712 the amplifiers shutdown in pairs.

When exiting shutdown, there is a 6µs delay before the amplifier output becomes active.

### **Power Supplies and Layout**

The AS1710/AS1712 can operate from a single 2.7 to 5.5V supply or from dual  $\pm$ 1.35 to  $\pm$ 2.5V supplies. Good design improves device performance by decreasing the amount of stray capacitance at the op amp inputs/outputs.

- For single-supply operation, bypass the power supply with a 0.1µF ceramic capacitor.

- For dual-supply operation, bypass each supply to ground.

- Decrease stray capacitance by placing external components close to the op amp pins, minimizing trace and lead lengths.

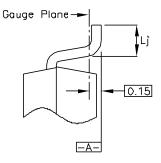

Lí

0.15

# 9 Package Drawings and Markings

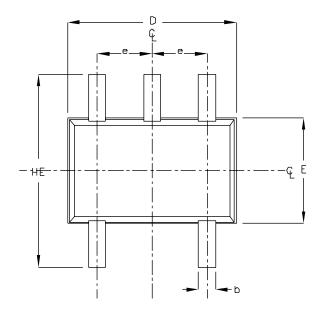

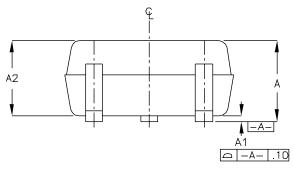

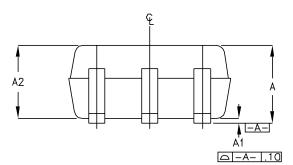

Figure 27. SC70-5 Package

Gauge Plane--

- 1. All dimensions are in millimeters.

- 2. Dimensions are inclusive of plating.

- 3. Dimensions are exclusive of mold flash and metal burr.

- 4. All specifications comply with *JEITA* SC88A and *JEDEC MO203*.

| Symbol | Min  | Max  |

|--------|------|------|

| е      | 0.65 | BSC  |

| D      | 1.80 | 2.20 |

| b      | 0.15 | 0.30 |

| Е      | 1.15 | 1.35 |

| HE     | 1.80 | 2.40 |

| Q1     | 0.10 | 0.40 |

| A2     | 0.80 | 1.00 |

| A1     | 0.00 | 0.10 |

| А      | 0.80 | 1.10 |

| С      | 0.10 | 0.18 |

| L      | 0.10 | 0.30 |

| Lj     | 0.26 | 0.46 |

-A-

Data Sheet - Package Drawings and Markings

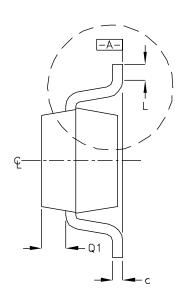

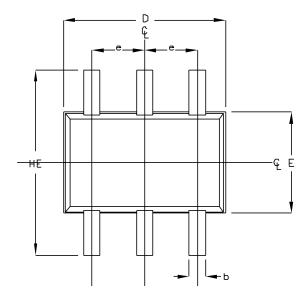

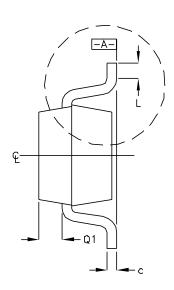

#### Figure 28. SC70-6 Package

#### Notes:

- 1. All dimensions are in millimeters.

- 2. Dimensions are inclusive of plating.

- 3. Dimensions are exclusive of mold flash and metal burr.

- 4. All specifications comply with *JEITA SC88* and *JEDEC MO203.*

| Symbol | Min  | Max  |  |  |

|--------|------|------|--|--|

| е      | 0.65 | BSC  |  |  |

| D      | 1.80 | 2.20 |  |  |

| b      | 0.15 | 0.30 |  |  |

| Е      | 1.15 | 1.35 |  |  |

| HE     | 1.80 | 2.40 |  |  |

| Q1     | 0.10 | 0.40 |  |  |

| A2     | 0.80 | 1.00 |  |  |

| A1     | 0.00 | 0.10 |  |  |

| А      | 0.80 | 1.10 |  |  |

| С      | 0.10 | 0.18 |  |  |

| L      | 0.10 | 0.30 |  |  |

| Lj     | 0.26 | 0.46 |  |  |

Data Sheet - Package Drawings and Markings

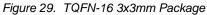

| aaa |      | 0.15    |      | 1, 2 |

|-----|------|---------|------|------|

| bbb |      | 0.10    |      | 1, 2 |

| CCC |      | 0.10    |      | 1, 2 |

| ddd |      | 0.05    |      | 1, 2 |

| b   | 0.18 | 0.25    | 0.30 | 1, 2 |

| А   | 0.70 | 0.75    | 0.80 | 1, 2 |

| A1  | 0.00 | 0.02    | 0.05 | 1, 2 |

| A3  |      | 0.20REF |      | 1, 2 |

| е   |      |         | 0.50 |      |

| Symbol | Min  | Тур  | Max  | Notes   |

|--------|------|------|------|---------|

| L1     | 0.03 |      | 0.15 | 1, 2    |

| D BSC  |      | 3.00 |      | 1, 2, 8 |

| E BSC  |      | 3.00 |      | 1, 2, 8 |

| D2     | 1.30 | 1.45 | 1.55 | 1, 2, 8 |

| E2     | 1.30 | 1.45 | 1.55 | 1, 2, 8 |

| L      | 0.30 | 0.40 | 0.50 | 1, 2, 8 |

| N      |      | 16   |      | 1, 2, 8 |

| ND     |      | 4    |      | 1, 2, 8 |

| NE     |      | 4    |      |         |

#### Notes:

- 1. Dimensioning and tolerancing conform to ASME Y14.5m-1994.

- 2. All dimensions are in millimeters while angle is in degrees (°).

- 3. N is the total number of terminals.

- 4. The terminal #1 identifier and terminal numbering convention shall conform to *JEDEC 95*, *SPP-002*. Details of terminal #1 identifier are optional, but must be located within the zone indicated. The terminal #1 identifier may be either a mold or marked feature.

- 5. Dimension b applies to metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip. If the terminal has the optional radius on the other end of the terminal, the dimension b should not be measured in that radius area.

- 6. Depopulation is possible in a symmetrical fashion.

- 7. Dimension b applies to metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip. If the terminal has the optional radius on the other end of the terminal, the dimension b should not be measured in that radius area.

- 8. ND and NE refer to the number of terminals on sides D and E respectively.

# **10 Ordering Information**

The device is available as the standard products shown in Table 6.

Table 6. Ordering Information

| Model        | Description                 | Delivery Form | Package       |

|--------------|-----------------------------|---------------|---------------|

| AS1710A-ASCT | Single Op Amp with Shutdown | Tape and Reel | SC70-6        |

| AS1710B-ASCT | Single Op Amp               | Tape and Reel | SC70-5        |

| AS1712A-AQFT | Quad Op Amp with Shutdown   | Tape and Reel | TQFN-16 3x3mm |

All devices are RoHS compliant and free of halogene substances.

## Copyrights

Copyright © 1997-2009, austriamicrosystems AG, Schloss Premstaetten, 8141 Unterpremstaetten, Austria-Europe. Trademarks Registered ®. All rights reserved. The material herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner.

All products and companies mentioned are trademarks or registered trademarks of their respective companies.

### Disclaimer

Devices sold by austriamicrosystems AG are covered by the warranty and patent indemnification provisions appearing in its Term of Sale. austriamicrosystems AG makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. austriamicrosystems AG reserves the right to change specifications and prices at any time and without notice. Therefore, prior to designing this product into a system, it is necessary to check with austriamicrosystems AG for current information. This product is intended for use in normal commercial applications. Applications requiring extended temperature range, unusual environmental requirements, or high reliability applications, such as military, medical life-support or life-sustaining equipment are specifically not recommended without additional processing by austriamicrosystems AG for each application. For shipments of less than 100 parts the manufacturing flow might show deviations from the standard production flow, such as test flow or test location.

The information furnished here by austriamicrosystems AG is believed to be correct and accurate. However, austriamicrosystems AG shall not be liable to recipient or any third party for any damages, including but not limited to personal injury, property damage, loss of profits, loss of use, interruption of business or indirect, special, incidental or consequential damages, of any kind, in connection with or arising out of the furnishing, performance or use of the technical data herein. No obligation or liability to recipient or any third party shall arise or flow out of austriamicrosystems AG rendering of technical or other services.

### **Contact Information**

Headquarters austriamicrosystems AG A-8141 Schloss Premstaetten, Austria

Tel: +43 (0) 3136 500 0 Fax: +43 (0) 3136 525 01

For Sales Offices, Distributors and Representatives, please visit:

http://www.austriamicrosystems.com/contact-us